AVR programuotojai. AVR derinimas grandinėje per JTAG ICE Kodėl verta rinktis JTAG programuotoją

1 Aprašymas

AVR JTAG yra prietaisų derinimo įrankis, pagrįstas Atmel AVR šeimos mikrovaldikliais. AVR JTAG yra pilnas Atmel AVR JTAG ICE analogas. Norėdami gauti daugiau informacijos apie tai, kaip AVR Studio veikia su AVR JTAG, galite naudoti Atmel dokumentus.

Norint dirbti su AVR JTAG, naudojama AVR Studio programa iš Atmel. AVR JTAG palaiko visus šeimos mikrovaldiklius, turinčius JTAG sąsają:

- ATmega16;

ATmega162;

ATmega169;

ATmega32;

ATMega323;

ATMega64;

ATmega128.

Naujų įrenginių palaikymas suteikiamas atnaujinus AVR JTAG programinę-aparatinę įrangą, kuri yra įtraukta į AVR Studio.

1 pav. Jungčių ir indikatorių vieta AVR JTAG plokštėje

Pristatymo turinys

Į AVR JTAG paketą įeina:

- AVR JTAG plokštė;

- maitinimo šaltinis;

- kabelis AVR JTAG prijungimui prie kompiuterio;

- kabelis AVR JTAG prijungimui prie derinamo įrenginio;

- CD su programine įranga ir informacine informacija.

2 pav. Lentos išvaizda

Ryšys

Kad AVR Studio automatiškai aptiktų AVR JTAG, prieš paleisdami AVR Studio turite prijungti AVR JTAG prie kompiuterio, tikslinio įrenginio ir tiekti AVR JTAG bei tikslinį įrenginį.

Prisijungimas prie kompiuterio

AVR JTAG jungiasi prie standartinio kompiuterio COM prievado. Prijungimui naudojamas 9 kontaktų „tiesus“ laidas (yra komplekte).

Kai AVR Studio paleidžiama, ji automatiškai ieško palaikomų įrenginių ir iš eilės pasiekia visus kompiuterio COM prievadus. Paieška bus sustabdyta, kai tik bus rastas palaikomas įrenginys. Pavyzdžiui, jei AVR Prog yra prijungtas prie COM1, o AVR JTAG yra prijungtas prie COM2, tada AVR Studio aptiks tik AVR Prog. Todėl paleisdami AVR Studio įsitikinkite, kad kiti jos palaikomi įrenginiai yra išjungti, arba paleidę AVR Studio rankiniu būdu nustatykite prievadą, prie kurio prijungtas AVR JTAG.

Jei COM prievadą, prie kurio prijungtas AVR JTAG, naudoja kitos programos (pavyzdžiui, terminalas), tada AVR Studio negalės aptikti AVR JTAG. Uždarykite šias programas prieš paleisdami AVR Studio.

Prisijungiama prie derinamo įrenginio

Norint prisijungti prie derinamo įrenginio, naudojamos 6 eilutės: TCK, TDO, TDI, TMS, VTref ir GND; prijungti šias linijas būtina, kad AVR JTAG tinkamai veiktų su derinamu įrenginiu.

Be to, nSRST liniją galima prijungti prie derinamo įrenginio (naudojama mikrovaldiklio atstatymo linijai valdyti ir stebėti). Šio signalo naudoti nereikia derinant, tačiau jei mikrovaldiklio programa nustato JTD bitą MCUCSR registre, JTAG sąsaja bus išjungta ir reikės, kad AVR JTAG galėtų valdyti mikrovaldiklio atstatymo liniją, kad ją įgalintų. .

3 pav. AVR JTAG prijungimas prie derinamo įrenginio

Maitinimo jungtis

AVR JTAG maitinamas išoriniu kintamosios srovės arba nuolatinės srovės maitinimo šaltiniu (įtraukta). Norint prijungti šaltinį prie AVR JTAG, naudojamas 2,5 mm lizdas. Nuolatinės srovės šaltinio poliškumas neturi reikšmės.

Kad AVR Studio aptiktų AVR JTAG, prieš pradedant derinimą būtina įjungti AVR JTAG ir derinamo įrenginio maitinimą (naudojant mygtuką Pradėti derinti AVR Studio).

- įjunkite derinamo įrenginio maitinimą;

- įjunkite AVR JTAG maitinimą;

- paleiskite AVR Studio.

Programinės įrangos atnaujinimas

AVR JTAG programinės įrangos atnaujinimas gali būti atliekamas automatiškai arba rankiniu būdu.

Automatinis atnaujinimas

Automatinis atnaujinimas įvyksta, jei AVR Studio nustato, kad su AVR Studio įtraukta programinės aparatinės įrangos versija yra naujesnė nei AVR JTAG programinės aparatinės įrangos versija. Tokiu atveju AVR Studio parodys atitinkamą pranešimą ir paragins atnaujinti programinę-aparatinę įrangą. Jei vartotojas sutinka atnaujinti programinę įrangą, AVR Studio parodo dialogo langą su programinės įrangos atnaujinimo instrukcijomis. Norėdami atnaujinti programinę įrangą, atlikite šiuos veiksmus:

- spustelėkite mygtuką "Gerai" AVR Studio dialogo lange;

- pasirodžiusiame dialogo lange AVR Prog spustelėkite mygtuką "Programa";

AVR JTAG programinės įrangos atnaujinimas baigtas.

Rankinis atnaujinimas

AVR JTAG programinę įrangą atnaujinti rankiniu būdu gali prireikti, jei automatinis programinės įrangos atnaujinimas buvo nutrauktas dėl kokios nors priežasties (maitinimo sutrikimas ir pan.). Tokiu atveju AVR Studio negalės aptikti AVR JTAG, sužinoti jo programinės įrangos versijos ir pradėti automatinius programinės įrangos atnaujinimus.

Norėdami rankiniu būdu atnaujinti programinę įrangą:

- išjunkite AVR JTAG maitinimą;

- nuimkite AVR JTAG plokštės trumpiklį;

- įjunkite AVR JTAG maitinimą;

- paleiskite AVR Prog programą;

- pasirinkite failą su plėtiniu .EBN programavimui iš JTAGICE aplanko, esančio aplanke, kuriame įdiegta AVR Studio;

- paspauskite mygtuką "Programa";

- baigę atnaujinti programinę įrangą, uždarykite langą AVR Prog;

- sumontuokite trumpiklį ant AVR JTAG plokštės;

- Įjunkite AVR JTAG.

AVR JTAG programinės įrangos rankinis atnaujinimas baigtas.

Kuriant ir derinant programas mikrovaldikliams, kyla klausimų, susijusių su programos programavimu ir derinimu realioje grandinėje. Jei programuojant AVR mikrovaldiklius nėra jokių ypatingų problemų, nes yra daug grandinių, skirtų programinei įrangai „pilti“ į kristalą, viena iš paprasčiausių tokių grandinių yra grandinė, vadinama „penkiais laidais“, tada derinant nėra tokio gausaus pasirinkimo. programa.

Norėdami derinti programą, galite naudoti tik dvi parinktis - programinės įrangos simuliatorių ir grandinės JTAG emuliatorių-programuotoją. Programinės įrangos treniruoklis, kaip taisyklė, negali atsižvelgti į visas grandinės veikimo ypatybes, tokias kaip išorinis poveikis, bendras veikimas su kitais įrenginiais ir kt. Naudojant JTAG aparatūros programuotojus-derintuvus, tampa įmanoma žingsnis po žingsnio derinti programą tiesiai pačiame mikrovaldiklyje, įdiegtame tiesiai į grandinę, peržiūrėti ir keisti visus mikrovaldiklio registrus, nustatyti lūžio taškus ir, žinoma, programuoti grandinėje. iš mikrovaldiklio. Bet originalo kaina AVR JTAG ICE MkII pagaminta „Atmel“ svyruoja apie 300 eurų, o jo analogas AVDRAGONAS masinės gamybos, tai kainuoja apie 3000 rublių, o tai yra labai brangu žmonėms, kurie kuria įrenginius AVR mikrovaldikliuose „sau“.

Bet, laimei, mums pavyko sukurti originalo kloną AVR JTAG ICE, kuris kainuoja žymiai pigiau nei originalas ir leidžia programuoti bei derinti AVR mikrovaldiklius su JTAG sąsaja.

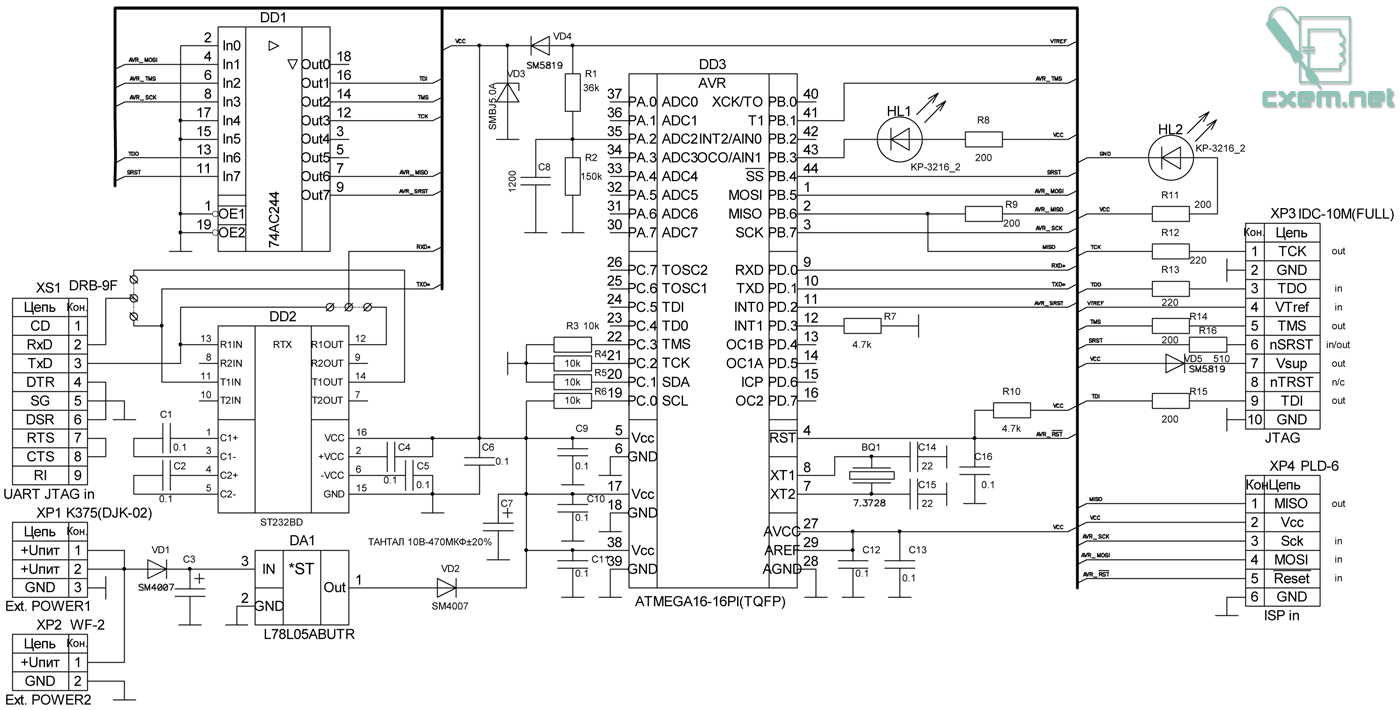

1 pav. AVR JTAG ICE klono grandinė

Elektros grandinės schema parodyta fig. 1. Šio JTAG pagrindas yra DD3 AVR ATMega16 mikrovaldiklis. DD2 MAX232 lustas veikia kaip RS232 sąsajos keitiklis į TTL UART lygius. DD1 lustas skirtas apsaugoti DD3 mikrovaldiklio įvesties ir išvesties grandines ir suderinti loginių lygių įtampą naudojant išorinį maitinimą.

JTAG maitinimą galima paimti iš derinamo įrenginio maitinimo grandinių per ketvirtąjį vTref XP3 kontaktą, taip pat galima naudoti išoriškai per XP1 ir XP2 jungtis. Išorinė įtampa gali būti nuo 7 iki 15 V. Naudojant išorinį maitinimo šaltinį, XP3 jungties vTref kaiščio prijungti nereikia.

LED HL2 rodo galios buvimą, HL1 yra JTAG veikimo režimas.

JTAG yra prijungtas prie mikrovaldiklio, kuris derinamas per standartinę dešimties kontaktų jungtį. Kurio prijungimo schema parodyta fig. 2.

2 pav. AVR JTAG ICE sujungimo su derinamu įrenginiu schema

Yra keletas JTAG programinės įrangos BootLoader įkrovos įkroviklių parinkčių, tačiau, mano nuomone, sėkmingiausią variantą padarė Vitalijus Krotevičius (Vit). Jo įkrovos įkroviklis labiausiai atkartoja patentuotą ir leidžia atnaujinti JTAG programinę-aparatinę įrangą tiesiai iš AVRStudio, neperkraunant JTAG ir neįjungiant programavimo režimo per BootStart. Jei neplanuojate atnaujinti JTAG programinės aparatinės įrangos, tuomet negalite paleisti įkrovos įkrovos, o tik „flash“ originalios programinės įrangos iš .

Norėdami „įjungti“ įkrovos įkroviklį į JTAG, galite naudoti AVReal, PonyProg, STK200, „penkių laidų“ programuotoją arba bet kurį kitą prieinamą ir suderinamą su AVR IPT. Programuotojas prijungtas prie ISP programavimo jungties XP4. Programinės aparatinės įrangos failas JTAG_ICE.hex.

Saugiklių programavimo pavyzdys parodytas 3 pav.

3 pav. AVR JTAG ICE saugiklių nustatymas

AVR JTAG ICE veikimo pavyzdys parodytas 4 paveiksle. Kaip pavyzdys buvo nuskaitytas ATMega128 parašas

4 pav. ATMega128 mikrovaldiklio parašo nuskaitymas naudojant AVR JTAG ICE

5 pav. Viršutinio PCB pėdsako sluoksnio vaizdas su pritaikytais elementais

6 pav. Apatinio PCB pėdsako sluoksnio vaizdas su pritaikytais elementais

Baigto įrenginio nuotraukos:

P.S. Spausdintinės plokštės schemą ir pėdsaką sukūrė straipsnio autorius, įkrovos įkroviklį naudojo Vitalijus Krotevičius (dar žinomas kaip Vit), programinė įranga buvo iš originalios AVRStudio.

Rašant šį straipsnį buvo naudojami šie šaltiniai:

1 http://onembedding.bialix.com/files/jtag_vit/

2. Oficialus AVR JTAG ICE vartotojo vadovas JTAGuserguide.pdf

Toliau galite atsisiųsti programinę-aparatinę įrangą ir PCB failus

Radioelementų sąrašas

| Paskyrimas | Tipas | Denominacija | Kiekis | Pastaba | Parduotuvė | Mano užrašų knygelė |

|---|---|---|---|---|---|---|

| DD1 | Buferio IC, vairuotojas | CD74AC244 | 1 | Į užrašų knygelę | ||

| DD2 | RS-232 sąsajos IC | MAX232 | 1 | ST232BD | Į užrašų knygelę | |

| DD3 | MK AVR 8 bitų | ATmega16 | 1 | ATmega16-16PI | Į užrašų knygelę | |

| DA1 | Linijinis reguliatorius | LM78L05 | 1 | Į užrašų knygelę | ||

| VD1, VD2 | Lygintuvo diodas | SM4007PL | 2 | Į užrašų knygelę | ||

| VD3 | Zenerio diodas | BZX55C5V1 | 1 | SMBJ5.0A | Į užrašų knygelę | |

| VD4, VD5 | Schottky diodas | SM5819PL | 2 | Į užrašų knygelę | ||

| HL1, HL2 | Šviesos diodas | KR-3216-2 | 2 | Į užrašų knygelę | ||

| C1, C2, C4-C6, C9-C13, C16 | Kondensatorius | 0,1 µF | 10 | Į užrašų knygelę | ||

| C3 | 1 | Į užrašų knygelę | ||||

| C7 | Elektrolitinis kondensatorius | 470 µF 10 V | 1 | Tantalas | Į užrašų knygelę | |

| C8 | Kondensatorius | 1200 pF | 1 | Į užrašų knygelę | ||

| C14, C15 | Kondensatorius | 22 pF | 2 | Į užrašų knygelę | ||

| R1 | Rezistorius | 36 kOhm | 1 | Į užrašų knygelę | ||

| R2 | Rezistorius | 150 kOhm | 1 | Į užrašų knygelę | ||

| R3-R6 | Rezistorius | 10 kOhm | 4 | Į užrašų knygelę | ||

| R4, R10 | Rezistorius | 4,7 kOhm | 2 | Į užrašų knygelę | ||

| R9, R11-R15 | Rezistorius | 200 omų | 7 | Į užrašų knygelę | ||

| R16 | Rezistorius |

Nežinau kaip jūs, bet aš laikau programuotoją vartojimo reikmenimis kurdamas įrenginius. Per 1,5 metų iš viso perdegė 3 programuotojai. Mūsų nuostabai, JTAG derintuvai, skirti AVR, yra brangūs. Be to, nėra iki galo aišku, kodėl gamintojas nori beveik 100 dolerių. Dėl to padariau keletą savadarbių derintuvų, užsisakiau pramoninei gamybai, o dabar naudoju.

Aš pats sukūriau grandinę, naudodamas šablonus iš interneto, kurių yra daug. Bet grandinė netilpo į vieną sluoksnį, todėl prasminga ją išdėlioti dar kartą; jei padarysite LUT viename sluoksnyje, jums reikės 4 laidų.

Dabar kalbant apie programinės aparatinės įrangos problemą, „AVR Studio“ apima galimybę paleisti programinę-aparatinę įrangą per įkrovos įkroviklį. Firminiai programuotojai turi įkrovos įkroviklį, kad būtų galima atnaujinti programinę įrangą. Bet mes mirksime valdiklį tiesiogiai naudodami programinę-aparatinę įrangą, nenaudodami įkrovos tvarkyklės, todėl pirmiausia jums reikės grandinės programuotojo ar kito derinimo priemonės. Tokiu atveju mikrovaldiklį reikia paleisti kitoje plokštėje, nes ši neturi ISP jungties, tačiau šiuo atveju tai nėra ypač brangu. Programinės įrangos failas miniIce.hex projekto viduje.

Schema:

Straipsnyje išsamiai aprašomas, pradedant informacijos paieškos procesu, mano populiaraus AVR JTAG ICE programuotojo (mk!!) grandinės versijos atsiradimas. Šis programuotojas įdomus tuo, kad jis skirtas AVR mikrovaldikliams ir turi įmontuotą JTAG. gali atlikti lusto derinimą, o tai neįmanoma naudojant programuotojus, turinčius universalią AVR ISP sąsają.

Norėjau susikurti ATMega16A/32A/64A/128/256 serijos 8 bitų AVR valdiklių derintuvą. Deja, mano turimi programuotojai gali per žemos įtampos ISP sąsają paleisti mikrovaldiklį, bet nemoka derinti. Tas pats pasakytina ir apie įsigytą – patį pirmąjį mano kolekcijoje – programuotoją iš parduotuvės ekits.ru. Todėl, šiek tiek paieškojęs internete, nusprendžiau susikurti sau JTAG programuotoją.

Taigi, pradėkime ieškoti informacijos internete. Kadangi kai kurias medžiagas jau peržiūrėjau internete, dabar tiesiog pateiksiu nuorodas su trumpu aprašymu..

EagleCAD taip pat turi pusiau oficialią svetainę eaglecad.ru ir ten taip pat yra mokymo programa, bet atrodo, kad ją palaiko entuziastas ir ne per daug atidžiai. Taip pat galbūt norėsite perskaityti keletą straipsnių iš svetainės chipenable.ru:

- EagleCAD. Elektroninės grandinės kūrimas.

- EagleCAD. Komponento kūrimas. 1 dalis .

- EagleCAD. Komponento kūrimas. 2 dalis.

Tęskime paiešką „RuNet“.

- Apie įterptąsias sistemas“, kurios, deja, kūrimas buvo nutrauktas 2006 m., yra straipsnis „JTAG for AVR“. Nors informacija yra pasenusi, kai kuriuos sprendimus dėl „tranzistoriaus-diodo“ laidų galima rasti iš medžiagos.

- Tiesiog puikus kūno komplektas, nors ir kitokiame programuotoje. Pavyzdys sekti. Nejuokauju. Cm. .

- Gerai žinomas ir gerbiamas šaltinis – svetainė „Litmetinis“ mane nudžiugino labai labai geru straipsniu tema: „AVR JTAG ICE Clone“ ir šis klonas gerokai skiriasi nuo to, apie ką galvojau anksčiau. Jo esmė ta pati – „Mega16A“ mikrovaldiklis, tačiau techninė įranga daug įspūdingesnė. Kad nepažeisčiau niekieno autorių teisių, pasiskolinu nuorodą į paveikslėlį.

Autorių lenta pasirodė esanti 48 x 40,6 mm, o tai įspūdinga. Tiesa, tam autoriai turėjo montuoti komponentus abiejose lentos pusėse. Ką. Aš taip pat tai padariau, kai norėjau sutaupyti :). Na, leiskite man pradėti analizuoti šią labai turtingą ir kompetentingą schemą. Mano mėgėjų požiūriu, žinoma.

- Nepriklausomas maitinimo šaltinis ant linijinio stabilizatoriaus. Ar aš įdiegsiu papildomą maitinimo šaltinį? USB prievadas, pagal standartą, turi maitinti tik įrenginius, kurių srovės suvartojimas yra iki 500 mA. Tiesą sakant, šiuolaikiniai USB prievadai yra dar galingesni. Šio tipo programuotojai neleidžia programuoti jokių procesorių, kurių įtampa didesnė nei 5 V. Santrauka: man nereikia papildomo maitinimo šaltinio.

- Naudojant 74FC244 buferio lustą. Tikrai taip. Pristatysiu buferinį lustą. Ir jei įmanoma, paskelbsiu galinėje pusėje :).

- Kojos nuo 19 iki 22 (vietinis JTAG MK) traukiamos į žemę per 10k rezistorius. Man, kaip ir visose anksčiau aptartose schemose, jos kabo. Sprendimas: aš padarysiu tą patį. Ekstremaliais atvejais 0805 rezistoriai neužima daug vietos (arba galite pridėti 0603 prie projekto) ir jums tiesiog nereikia jų lituoti. Apskritai ant plokščių dažnai matau nelituotų komponentų. Ir aš manau, kad tai yra normalu. Rezervas, kuris gali būti naudojamas arba gali būti paliktas arba pakeistas džemperiu.

- MK maitinimo prievadai „pakabinami“ labai atsargiai. Bet aš tai jau suplanavau :).

- Išėjimo grandinėse naudojami 200 ir 220 omų rezistoriai. Ankstesnėse schemose 100 omų. Planavau naudoti labiau "pažįstamus" 68 omus... pagalvosiu ir pabandysiu.

- Yra dar du JTAG kaiščiai. Be to, išvedami VTRef ir Vsup signalai - maitinimas į tikslinę plokštę. Neturėsiu kito maitinimo šaltinio, išskyrus 5 voltus.

- Turiu apsauginį zenerio diodą ant MK maitinimo šaltinio.

(Vėliau pastaba. Plokštės išdėstyme nepateikiau jokių kontaktinių trinkelių ar trumpiklių, įžeminančių įjungimo išvestį. Todėl jei kada nors vis tiek norėsite detaliau suprasti protokolo programinės įrangos įgyvendinimo niuansus ir prijungti buferio grandinės kaiščių valdymą , turėsite atlikti pakeitimus. Ne, manau, kad tai bus greitai.)

Pakeliui braižome schemą, iškart įterpdami kai kurias mintyse klaidžiojančias idėjas.

Mano takelių maršrutizavimo parinktis pasirodė tokia (išvesties komponentai: USB-B, kvarco rezonatorius, kaiščiai - nukreipti į vieną pusę, plokštė nukreipiama iš kitos pusės):

3D modelis turėtų atrodyti maždaug taip:

Šiuo metu sandėlyje neturiu Mega16A arba 7,3728 MHz „egzotiško“ kvarco. Todėl praktinis schemos išbandymas kol kas atidedamas. Kai tik pasirodys komponentai, straipsnis bus tęsiamas.

Taigi, užsakyti komponentai pagaliau buvo pristatyti ir aš turėjau laiko atsiduoti savo pomėgiui. Mano klono surinktos lentos išvaizda atrodo taip:

Vaizdas iš viršaus

Vaizdas iš apačios. Palyginti su „SketchUp“ susintetinta lenta, tikroji plokštė buvo vizualiai apversta – viršus ir apačia buvo sukeisti vietomis. Bent jau tai galima spręsti pagal asimetriškai išdėstytą modulį CP2102.

Radau nuorodą į komercinį šio programuotojo įgyvendinimą. Jie prašo daugiau nei 35 USD. Tačiau...

DV164045- didelės spartos ir ekonomiškas įrankis, skirtas PIC mikrovaldiklių ir dsPIC skaitmeninių signalų valdiklių iš Microchip programavimui ir derinimui grandinėje. Didelį veikimo greitį užtikrina produkte naudojamas 300 MHz 32 bitų MCU su 2 MB RAM ir didelės spartos FPGA, kuri užtikrina greitesnį ryšį, atsisiuntimą ir derinimą, lyginant su ankstesnėmis įrenginio versijomis. Derinimas ir programavimas atliekami naudojant galingą, bet lengvai naudojamą MPLAB X IDE grafinę sąsają. MPLAB ICD4 jungiasi prie jūsų kompiuterio per USB 2.0 HS sąsają ir prie tikslinės plokštės derinimo antraštės, kuri taip pat suderinama su MPLAB ICD3 ir MPLAB in-circuit emuliatoriai REAL ICE™. Be to, MPLAB ICD4 gali dirbti su JTAG sąsaja.

MPLAB 4 programuotojas/debugger šiuo metu palaiko daug, bet ne visus, PIC ir dsPIC. Programinė įranga nuolat atnaujinama, kad būtų išplėstas palaikomų mikrovaldiklių sąrašas. Adresas, kuriuo galite prašyti pagalbos dėl prioritetinių lustų arba pranešti apie problemas: [apsaugotas el. paštas].

Jei turite įdiegtą MPLAB X IDE, palaikomų lustų sąrašą galite rasti diegimo katalogo aplanke „docs“. Failo pavadinimas yra „Device Support.htm“. Be to, sąrašą galima atsisiųsti iš nuorodos http://www.microchip.com/mlabx-ide-release-notes.

Ryžiai. Grandinėje programuotojas / derintuvas DV164045

Skiriamieji bruožai:

- Viso greičio realiojo laiko emuliacija:

- Sukurta palaikyti didelės spartos procesorius, veikiančius maksimaliu greičiu

- Derinti programas savo lentoje realiuoju laiku

- Patikima sąsaja:

- Pridėta derinimo tvarkyklių grandinės apsauga, siekiant apsaugoti jas nuo tikslinės plokštės galios viršįtampių

- Stebėkite VDD ir VPP, kad apsaugotumėte nuo viršįtampių. Visos linijos yra apsaugotos nuo viršsrovių

- Saugus maitinimas iki 1 A su papildomu maitinimo šaltiniu

- Mikroschemos standartinis ryšys plius JTAG:

- Yra su standartine „Microchip“ derinimo antrašte. Galima naudoti JTAG

- Suderinamumas:

- Palaiko visas MPLAB ICD 3 jungtis

- Nešiojamas USB maitinimo įrenginys; RoHS atitiktis:

- Plokštė yra patvariame juodame dėkle su matiniu aliuminio dangteliu ir šviesos diodų linija, rodančia derinimo būseną.

- Maitinamas per USB prievadą, nereikia išorinio maitinimo

- CE ir RoHS atitiktis

- Platus emuliacijos įtampų diapazonas:

- Palaiko tikslinę įtampą nuo 20 V iki 5,5 V

- Didelės spartos programavimas:

- Greitas programinės įrangos paleidimas iš naujo, kad būtų galima greitai derinti / perprogramuoti grandinėje

- Apima programuojamą derinimo greičio nustatymą, kad būtų galima optimizuoti programavimą

- Bandymo sąsajos modulis:

- Apima grįžtamojo ryšio modulį, skirtą derinimo prievadui ir kabeliui išbandyti

- Lengva prižiūrėti ir atnaujinti funkcijas:

- Pridėkite naujų lustų ir funkcijų palaikymą įdiegę naujausią MPLAB X IDE versiją, kurią galima nemokamai atsisiųsti adresu www.microchip.com/mplabx

- Programinės įrangos atnaujinimas naudojant MPLAB X IDE

- Ekonominis efektyvumas:

- Funkcijos ir našumas prilygsta panašioms emuliacijos sistemoms

- Galingas derinimas:

- Galingas derinimas naudojant MPLAB X IDE

- Palaiko kelis pertraukos taškus, chronometrą ir šaltinio kodo derinimą

- Galimybė pasirinkti tikslinės sąsajos ištraukimą MPLAB X IDE redaktoriuje, kad būtų galima greitai modifikuoti / derinti

- Sistemos reikalavimai:

- MPLAB X IDE vers. 4.00 ar daugiau

- Galimas USB prievadas

- „Microsoft Windows® 7“ ar naujesnė versija, „Mac OSX®“ ir „Linux®“.